认识存储产品

存储产品包括DDR、NAND、HBM。

DDR

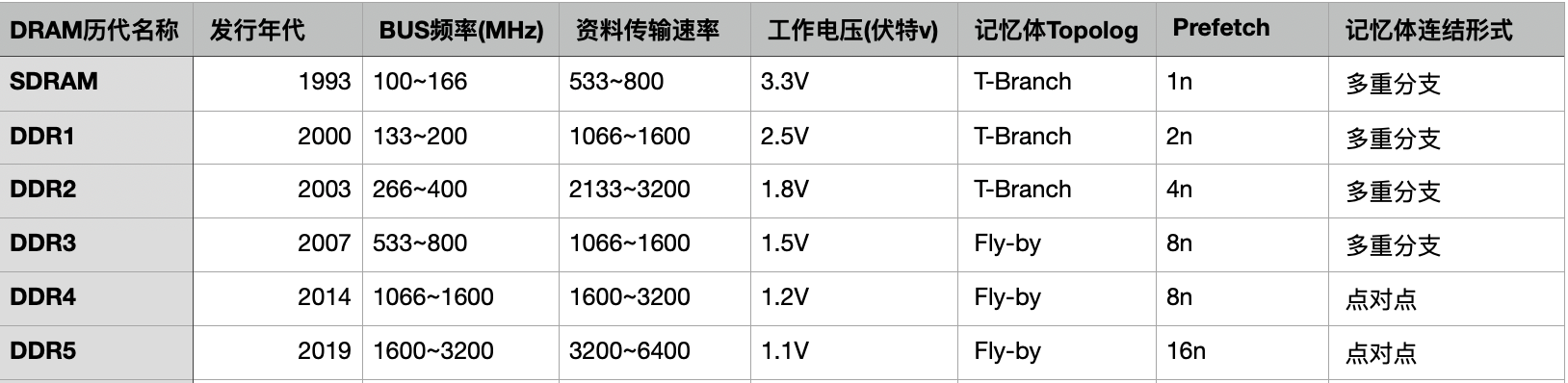

DDR全称:Double Data Rate Synchronous Dynamic Random Access Memory(双倍数据率同步动态随机存取存储器),中文俗称“内存”。自1997年第1代问世以来,已发展至第5代DDR5,走过二十多年历程。

DDR实现原理

其核心机制包括预取技术、延时锁定回路(DLL)及低工作电压设计。

SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

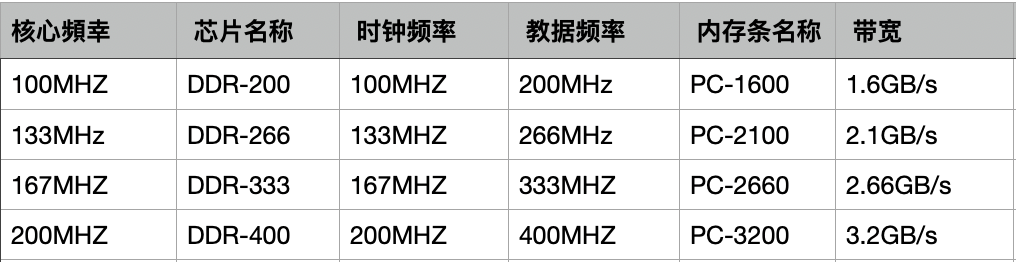

DDR内存的频率可以用工作频率和等效频率两种方式表示,工作频率是内存颗粒实际的工作频率,但是由于DDR内存可以在脉冲的上升和下降沿都传输数据,因此传输数据的等效频率是工作频率的两倍。

DDR使用场景

DDR:英文全称Double Data Rate Synchronous Dynamic Random Access Memory。它主要应用在普通内存条。

LPDDR:英文全称Low Power Double Data Rate Synchronous Dynamic Random Access Memory。它主要应用在智能手机,智能手表等对功耗,体积敏感得产品。

GDDR:英文全称Graphics Double Data Rate Synchronous Dynamic Random Access Memory。主要用于高速图像处理的场合,比如计算机的显卡中,可以简单理解为专门为显卡而做的DDR内存,这种内存与普通DDR相比,拥有更高的时钟频率和更小的发热量。

DDR系列产品

DDR有以下系列产品。

DDR1

老的存储技术 DDR 称为 DDR1

DDR1的预取为2bit

DDR2

DDR2在DDR1内存技术的基础上加以改进,从而其传输速度更快,耗电量更低,散热性能更优良。

DDR2内存拥有两倍于上一代DDR内存预读取能力(即:4bit数据预读取)。

DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

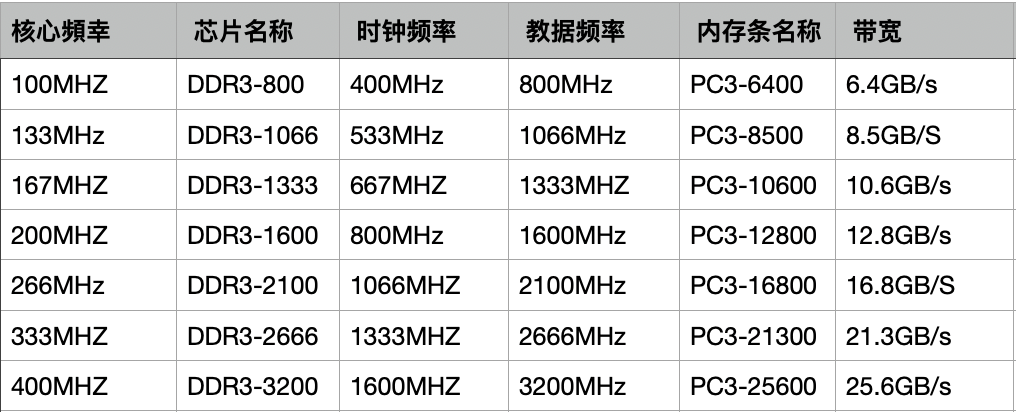

DDR3

DDR3的预取为8bit,突发传输周期(Burst Length,BL)也固定为8。

DDR3新增的重置(Reset)功能和ZQ校准功能。

DDR4

DDR4工作电压为1.2V,功耗更低,最大支持内存容量为64GB,最大带宽为256GB/s。

三星电子2011年1月4日宣布,已经完成了第一款DDR4DRAM规格内存条的开发,并采用30nm级工艺制造了首批样品。

DDR5

DDR5工作电压为1.1V,功耗更低,最大支持内存容量为128GB,最大带宽可达近1TB/s。

2017年6月,JEDEC宣称,下一代内存标准DDR5将亮相,并预计在2018年完成最终的标准制定。

2017年9月22日,Rambus宣布在实验室中实现完整功能的DDR5 DIMM芯片,预期将在2019年开始量产。

2018年10月,Cadence和美光公布了自己的DDR5内存研发进度,两家厂商已经开始研发16GB DDR5产品,并计划在2019年年底之前实现量产目标。

2020年7月,JEDEC协会正式公布了DDR5标准,起步4800MHz,未来可以达到6400MHz。

2020年10月,韩国存储巨头SK海力士宣布,正式发布全球第一款DDR5内存。

2021年1月,嘉合劲威率先布局DDR5内存模组。

2021年4月26日,嘉合劲威首批DDR5内存条批量生产下线。

2021年12月,SK海力士宣布提供业界内 DRAM 单一芯片容量最大的 24Gb DDR5 样品。

2022年10月,HKEPC 拿到十铨 DDR5-7800 内存条,这是已发布的最高 DDR5 内存频率。

2023年5月18日,三星电子宣布其采用12纳米级工艺技术的16Gb DDR5 DRAM已开始量产。

2023年11月28日,据长鑫存储技术有限公司官网显示,长鑫存储推出了最新LPDDR5 DRAM存储芯片,是国内首家推出自主研发生产的LPDDR5产品的品牌,实现了国内市场零的突破。

2024年12月,首款基于国产颗粒的DDR5内存正式发布。

NAND

NAND闪存(外文名:NAND Flash)是由东芝公司于1989年提出的非易失性闪存存储器,通过非线性宏单元模式与垂直排列半导体单元提升存储密度,支持以页(512字节)为单位读写数据,主要应用于U盘、移动设备及数据中心。

NAND使用场景

NAND是一种非易失性闪存,可以在存储数据后,断电了仍然能使数据继续存储。这一特性使得NAND成为外置设备、移动便携设备、消费电子产品内置存储的理想选择,例如手机和数码相机的内置存储便可以采用NAND闪存,固态硬盘、移动固态硬盘、存储卡、USB闪存盘这些也都是由NAND闪存技术而诞生和发展。

NAND发展历程

2025年11月,三星电子在国际期刊《自然》发表关于铁电材料与氧化物半导体融合的NAND闪存技术,实现功耗降低96%。该系统解决了高密度存储与低功耗矛盾,为人工智能数据中心及移动终端能效提升提供新路径。

三星计划2026年量产430层V10 NAND,SK海力士已量产321层2Tb QLC闪存并布局400+层生产,美光第九代采用276层架构使存储密度提升40%。

NAND产品类型

NAND闪存的常见类型有SLC、MLC、TLC 和QLC等。不同类型的闪存,其结构特性、单元位数、耐久性等是不同的,其中耐久性是由闪存单元在开始磨损前可以完成的程序擦写(P/E)周期数量来决定的,擦除和写入一个单元的过程便是一个P/E周期,P/E周期的标称数值越高,则表示该闪存颗粒可擦写的次数越高,即其耐久性越高。

SLC

SLC NAND的每个单元存储一位信息,0或1,写入和检索数据都很快,性能最佳,耐久性最高,提供高达10万个P/E周期,但是因为该类型闪存低数据密度的特性也让该SLC闪存最贵。耐久性强使得SLC在对读写耐久度要求很高的行业得以应用,如服务器、军工等。

MLC

MLC NAND属于多级单元,每个单元存储2个位。MLC的数据密度比SLC要高,可以有更大的存储容量,拥有1万个P/E周期,因而耐久性比SLC低。MLC在服务器、工规级应用较多。

TLC

TLC NAND为三级单元,每个单元存储3个位,P/E周期降至最高3000个。

QLC

QLC NAND为4级单元,每个单元存储4个位,性能和耐久性比TLC要差,代表耐久性方面的P/E周期只有1000个,但价格更便宜。目前已有消费级的大容量SSD采用QLC NAND闪存颗粒,例如致态Ti600、Crucial英睿达P310等固态硬盘就采用了QLC类型的闪存。

各类型对比

速度价格对比排序:SLC > MLC > TLC > QLC > PLC

容量大小对比排序:PLC > QLC > TLC > MLC > SLC

HBM

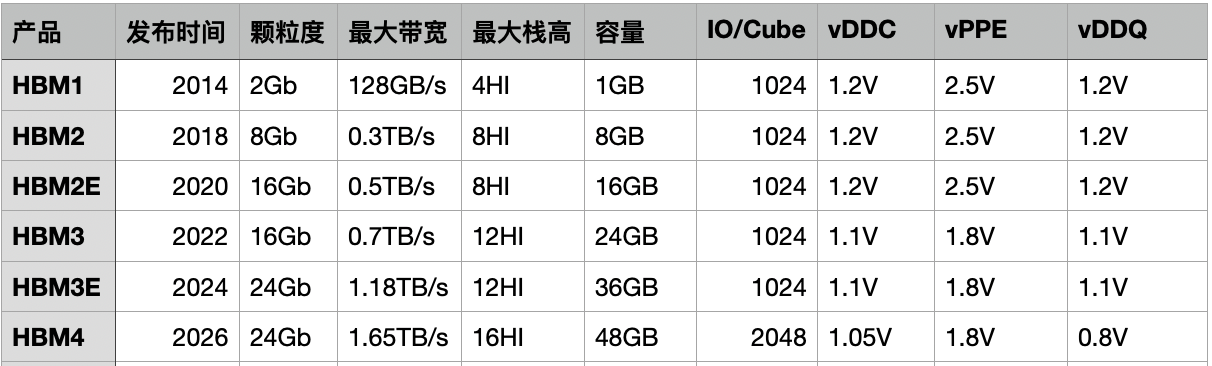

高带宽存储器(High Bandwidth Memory,HBM)是超微半导体和SK Hynix发起的一种基于3D堆栈工艺的高性能DRAM。

HBM实现原理

HBM通过垂直堆叠多个DRAM芯片,利用TSV技术实现高速互联,形成大容量、高位宽的内存阵列。

通过宽接口总线、多通道并行传输及缩短数据路径等方式,实现远超传统内存的带宽。

HBM使用场景

相较于传统2D DRAM,其带宽显著提升,同时降低单位数据能耗。适用于高存储器带宽需求的应用场合,像是图形处理器、网络交换及转发设备,例如:

(1)AI服务器:用于AI模型训练与推理,快速传输海量数据,加速模型运算,如英伟达H100、H200等GPU搭载HBM用于AI服务器 。

(2)数据中心:支撑云计算、大数据分析等业务,满足数据快速读写与交互,提升数据中心运营效率。

(3)超级计算机:在科学研究、气象预测、模拟仿真等领域,HBM提供高带宽和大容量内存支持 。

(4)GPU加速卡:如AMD和NVIDIA的高端显卡,搭配HBM显存,实现高分辨率、高帧率图形渲染 。

(5)游戏主机:未来可能应用HBM提升游戏加载速度、画面质量与流畅度 。

(6)自动驾驶:处理传感器采集的大量数据,实现快速决策与响应,保障驾驶安全。

(7)边缘计算:在边缘设备实现低延迟数据处理,满足实时性应用需求。

(8)网络设备:如交换机、路由器等,提高数据转发速度,应对网络流量增长。

(9)医疗影像处理:快速处理高分辨率医学影像数据,辅助医生诊断。

(10)金融交易系统:满足高频交易中对数据处理速度和准确性要求。

HBM产品的挑战

演进过程中面临挑战:芯片堆叠工艺难度增加、散热问题愈发严峻、制造成本居高不下。

解决挑战的技术方向:研发新型散热材料与结构、改进芯片制造工艺、优化封装流程。

HBM系列产品

HBM出现了以下系列产品

HBM1

2013年10月HBM成为了JEDEC通过的工业标准,实现初步3D堆叠,提供约128GB/s带宽 。

HBM2

HBM2于2016年1月成为工业标准,HBM2引入伪通道(Pseudo Channel)、隐式预充电操作和ECC存储等新功能,带宽提升至256GB/s以上 。

NVIDIA在该年发表的新款旗舰型Tesla运算加速卡 —— Tesla P100、AMD的Radeon RX Vega系列、Intel的Knight Landing也采用了HBM2。

HBM3

2022年1月,JEDEC发布了HBM3新标准 JESD238。

HBM3 标准提出了多项增强功能,包括支持更大的密度、更高速运算、更高的 Bank 数、更高的可靠性、可用性、可维护性 (RAS) 功能、低功耗接口和新的时钟架构。

HBM3带宽可达410GB/s以上。

HBM3E是HBM3扩展版本,速率达8Gbps,最高每秒可处理1.15TB数据。

HBM3 存储器很快就被用于 HPC 应用,例如 AI、图形、网络,甚至可能用于汽车。

行业即将生产12层高的HBM3E(36GB内存),但仍在推动技术边界,向16层或更高堆叠的HBM4发展。为了在提高散热和能效的同时满足更高密度芯片的尺寸要求,行业正在考虑在未来的HBM节点中通过直接连接铜垫实现混合粘接(Hybrid Bonding)。这将是对目前生产的微凸点技术的重大创新。尽管用于高性能计算的芯片小块集成的亚10微米间距的芯片到晶圆混合粘接已经投入生产,但由于在更低温度下堆叠的要求,亚20微米间距的HBM的挑战要大得多。

HBM4

HBM4预计接口宽度达2048位,单堆栈带宽2TB/s,容量36~48GB/堆栈。

HBM4/4e将继续与AI GPU/ASIC一道成为AI 超算时代的“主粮”。

HBM4/4e 不只是容量升级(更大单堆容量)、更是带宽和能效的阶跃——对谷歌TPU、英伟达Blackwell/Rubin架构这类高端AI芯片来说,HBM已经成为性能上限的核心瓶颈。谁先把HBM4量产、良率和成本打下来,谁就牢牢卡在AI算力产业链利润最丰厚的位置之一。

2025年3月SK海力士出货全球首款12层HBM4样品。

2025年美光HBM4完成送样测试。

存储产业发展

全球持续井喷式扩张的AI训练/推理算力需求全面带动DRAM/NAND系列存储产品需求指数级扩张。

在这轮以AI大模型更新迭代以及AI数据中心扩建/新建为核心的史无前例AI投资周期中,英伟达/博通/AMD等核心AI算力组件厂商们无疑是最大赢家;紧随其后的,则是以HBM为代表的高端存储器供应商(SK海力士、三星以及美光等),以及服务于AI数据中心的企业级高性能存储厂商(近线HDD 与数据中心SSD)。

美日韩三国争霸

1970年,英特尔发明了世界上第一款DRAM存储芯片,容量为1KB,售价为10美元。

1975年,韩国三星掌门人决定进入半导体领域,收购韩国第一家晶圆厂,更名为三星半导体。

1976年,日本启动超大规模集成电路计划,联合企业集中突破DRAM内存技术。

1978年,韩国三星经过8年的投资和夜以继日的研究,成功研制出了64KB的DRAM。

1981年,韩国政府推出半导体工业振兴计划,向半导体产业投入了3.46亿美元的政策性贷款,带动民间超20亿美元的投资。

20世纪80年代,存储器还是日本和美国的天下,但是美国在和日本的芯片竞争中节节败退。1981年,日本NEC率先完成256KB DRAM的研发,此后最新一代内存芯片始终由日本企业来主导。从1980~1990年,美国半导体份额从70%萎缩到20%,而日本半导体份额从25%上升到65%。美国原本扶持日本电子产业是为了找一个廉价的代工厂,但是日本学会了技术,靠着成本优势吸收美国的市场份额。美国在1985年和日本签订广场协议,1986年发起反倾销调查,1987年对日进口的电子产品加100%关税。在这些操作之下,日本半导体产业遭受重创,全球市场份额从1992年的67%降到2002年的12%。

1983~1986年,美国向韩国提供技术支持、市场准入优惠和人才支持。在美国扶持下,韩国半导体市场份额从1986年的2%,到1990年10%,再到2010年的60%。基本上让韩国吸收了日本的市场份额。

存储产业巨头

市场份额

韩国占据了存储市场70%市场份额。

存储是韩国的核心支柱产业。2024年,半导体出口占韩国总出口的31%,半导体产业占韩国GDP的12%,其中,65%以上都是存储芯片。

三星电子(韩国)

SK海力士(韩国)

SK海力士的HBM4存储系统在2026年下半年有望实现 “跨越点”——即出货量占总HBM销量的50%+,预计基于更先进1c-node 工艺的HBM4e预计将在 2026年末至2027年初上市。

美光科技(MU,美国)

美国芯片制造商美光科技公司将斥资1.5万亿日元(96亿美元)在日本西部建立一家工厂,生产用于人工智能的存储芯片。知情人士称,这家新工厂将生产高带宽内存(HBM)芯片。从2026年5月份开始,美光将在其现有的广岛工厂内建设该工厂,计划在2028年左右开始HBM出货。